kstars

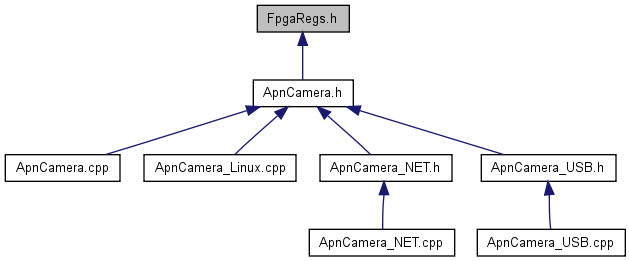

FpgaRegs.h File Reference

Go to the source code of this file.

Define Documentation

| #define FPGA_BIT_AD_SIMULATION 0x8000 |

Definition at line 60 of file FpgaRegs.h.

| #define FPGA_BIT_ARRAY_DIGITIZE 0x1000 |

Definition at line 109 of file FpgaRegs.h.

| #define FPGA_BIT_ARRAY_FASTDUMP 0x4000 |

Definition at line 110 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_AD_CONFIG 0x8000 |

Definition at line 33 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_CLEAR_ALL 0x0010 |

Definition at line 27 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_DAC_LOAD 0x4000 |

Definition at line 32 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_DARK 0x0002 |

Definition at line 19 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_END_EXPOSURE 0x0080 |

Definition at line 28 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_EXPOSE 0x0001 |

Definition at line 18 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_FLUSH 0x0010 |

Definition at line 22 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_RAMP_TO_AMBIENT 0x0400 |

Definition at line 30 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_RAMP_TO_SETPOINT 0x0200 |

Definition at line 29 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_RESET 0x0002 |

Definition at line 26 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_START_TEMP_READ 0x2000 |

Definition at line 31 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_TDI 0x0008 |

Definition at line 21 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_TEST 0x0004 |

Definition at line 20 of file FpgaRegs.h.

| #define FPGA_BIT_CMD_TRIGGER_EXPOSE 0x0020 |

Definition at line 23 of file FpgaRegs.h.

| #define FPGA_BIT_DAC_SELECT_ONE 0x0100 |

Definition at line 59 of file FpgaRegs.h.

| #define FPGA_BIT_DAC_SELECT_ZERO 0x0080 |

Definition at line 58 of file FpgaRegs.h.

| #define FPGA_BIT_DELAY_MODE 0x0008 |

Definition at line 39 of file FpgaRegs.h.

| #define FPGA_BIT_DIGITIZATION_RES 0x0400 |

Definition at line 46 of file FpgaRegs.h.

| #define FPGA_BIT_DISABLE_H_CLK 0x0040 |

Definition at line 42 of file FpgaRegs.h.

| #define FPGA_BIT_DISABLE_SHUTTER 0x1000 |

Definition at line 48 of file FpgaRegs.h.

| #define FPGA_BIT_FORCE_SHUTTER 0x0800 |

Definition at line 47 of file FpgaRegs.h.

| #define FPGA_BIT_HALT_DISABLE 0x0100 |

Definition at line 44 of file FpgaRegs.h.

| #define FPGA_BIT_HCLAMP_ENABLE 0x0008 |

Definition at line 54 of file FpgaRegs.h.

| #define FPGA_BIT_HRAM_ENABLE 0x0020 |

Definition at line 56 of file FpgaRegs.h.

| #define FPGA_BIT_HSKIP_ENABLE 0x0010 |

Definition at line 55 of file FpgaRegs.h.

| #define FPGA_BIT_LED_AT_TEMP 0x0080 |

Definition at line 133 of file FpgaRegs.h.

| #define FPGA_BIT_LED_DISABLE 0x0001 |

Definition at line 36 of file FpgaRegs.h.

| #define FPGA_BIT_LED_EXPOSE 0x0001 |

Definition at line 126 of file FpgaRegs.h.

| #define FPGA_BIT_LED_EXPOSE_DISABLE 0x0020 |

Definition at line 41 of file FpgaRegs.h.

| #define FPGA_BIT_LED_EXT_SHUTTER_INPUT 0x0020 |

Definition at line 131 of file FpgaRegs.h.

| #define FPGA_BIT_LED_EXT_START_READOUT 0x0040 |

Definition at line 132 of file FpgaRegs.h.

| #define FPGA_BIT_LED_EXT_TRIGGER 0x0010 |

Definition at line 130 of file FpgaRegs.h.

| #define FPGA_BIT_LED_FLUSHING 0x0004 |

Definition at line 128 of file FpgaRegs.h.

| #define FPGA_BIT_LED_IMAGE_ACTIVE 0x0002 |

Definition at line 127 of file FpgaRegs.h.

| #define FPGA_BIT_LED_TRIGGER_WAIT 0x0008 |

Definition at line 129 of file FpgaRegs.h.

| #define FPGA_BIT_P_CLK_MODE 0x0010 |

Definition at line 40 of file FpgaRegs.h.

| #define FPGA_BIT_PAUSE_TIMER 0x0002 |

Definition at line 37 of file FpgaRegs.h.

| #define FPGA_BIT_RATIO 0x0004 |

Definition at line 38 of file FpgaRegs.h.

| #define FPGA_BIT_SHUTTER_AMP_CONTROL 0x0080 |

Definition at line 43 of file FpgaRegs.h.

| #define FPGA_BIT_SHUTTER_MODE 0x0200 |

Definition at line 45 of file FpgaRegs.h.

| #define FPGA_BIT_SHUTTER_SOURCE 0x4000 |

Definition at line 50 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_DATA_HALTED 0x0004 |

Definition at line 156 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_FLUSHING 0x0010 |

Definition at line 158 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_IMAGE_DONE 0x0008 |

Definition at line 157 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_IMAGE_EXPOSING 0x0001 |

Definition at line 154 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_IMAGING_ACTIVE 0x0002 |

Definition at line 155 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_PATTERN_ERROR 0x0080 |

Definition at line 161 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_SHUTTER_OPEN 0x0040 |

Definition at line 160 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_TEMP_ACTIVE 0x8000 |

Definition at line 165 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_TEMP_AT_TEMP 0x4000 |

Definition at line 164 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_TEMP_REVISION 0x2000 |

Definition at line 163 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_TEMP_SUSPEND_ACK 0x0100 |

Definition at line 162 of file FpgaRegs.h.

| #define FPGA_BIT_STATUS_WAITING_TRIGGER 0x0020 |

Definition at line 159 of file FpgaRegs.h.

| #define FPGA_BIT_TEMP_SUSPEND 0x2000 |

Definition at line 49 of file FpgaRegs.h.

| #define FPGA_BIT_TEST_MODE 0x8000 |

Definition at line 51 of file FpgaRegs.h.

| #define FPGA_BIT_VRAM_ENABLE 0x0040 |

Definition at line 57 of file FpgaRegs.h.

| #define FPGA_MASK_AD_GAIN 0x07FF |

Definition at line 148 of file FpgaRegs.h.

| #define FPGA_MASK_CAMERA_ID 0x007F |

Definition at line 180 of file FpgaRegs.h.

| #define FPGA_MASK_FAN_SPEED_CONTROL 0x0FFF |

Definition at line 94 of file FpgaRegs.h.

| #define FPGA_MASK_INPUT_VOLTAGE 0x0FFF |

Definition at line 172 of file FpgaRegs.h.

| #define FPGA_MASK_IO_PORT_ASSIGNMENT 0x003F |

Definition at line 121 of file FpgaRegs.h.

| #define FPGA_MASK_IO_PORT_DATA 0x003F |

Definition at line 151 of file FpgaRegs.h.

| #define FPGA_MASK_IO_PORT_DIRECTION 0x003F |

Definition at line 118 of file FpgaRegs.h.

| #define FPGA_MASK_LED_ILLUMINATION 0x0FFF |

Definition at line 95 of file FpgaRegs.h.

| #define FPGA_MASK_LED_SELECT_A 0x000F |

Definition at line 124 of file FpgaRegs.h.

| #define FPGA_MASK_LED_SELECT_B 0x00F0 |

Definition at line 125 of file FpgaRegs.h.

| #define FPGA_MASK_SUBSTRATE_ADJUST 0x0FFF |

Definition at line 96 of file FpgaRegs.h.

| #define FPGA_MASK_TEMP_PARAMS 0x0FFF |

Definition at line 145 of file FpgaRegs.h.

| #define FPGA_MASK_VBINNING 0x0FFF |

Definition at line 108 of file FpgaRegs.h.

| #define FPGA_REG_A1_ROW_COUNT 30 |

Definition at line 101 of file FpgaRegs.h.

| #define FPGA_REG_A1_VBINNING 31 |

Definition at line 102 of file FpgaRegs.h.

| #define FPGA_REG_A2_ROW_COUNT 32 |

Definition at line 103 of file FpgaRegs.h.

| #define FPGA_REG_A2_VBINNING 33 |

Definition at line 104 of file FpgaRegs.h.

| #define FPGA_REG_A3_ROW_COUNT 34 |

Definition at line 105 of file FpgaRegs.h.

| #define FPGA_REG_A3_VBINNING 35 |

Definition at line 106 of file FpgaRegs.h.

| #define FPGA_REG_AD_CONFIG_DATA 62 |

Definition at line 147 of file FpgaRegs.h.

| #define FPGA_REG_CAMERA_ID 100 |

Definition at line 179 of file FpgaRegs.h.

| #define FPGA_REG_CLAMP_COUNT 13 |

Definition at line 75 of file FpgaRegs.h.

| #define FPGA_REG_COMMAND_A 0 |

Definition at line 17 of file FpgaRegs.h.

| #define FPGA_REG_COMMAND_B 1 |

Definition at line 25 of file FpgaRegs.h.

| #define FPGA_REG_FAN_SPEED_CONTROL 25 |

Definition at line 91 of file FpgaRegs.h.

| #define FPGA_REG_FIFO_DATA 98 |

Definition at line 176 of file FpgaRegs.h.

| #define FPGA_REG_FIFO_EMPTY_COUNT 103 |

Definition at line 185 of file FpgaRegs.h.

| #define FPGA_REG_FIFO_FULL_COUNT 102 |

Definition at line 184 of file FpgaRegs.h.

| #define FPGA_REG_FIFO_STATUS 99 |

Definition at line 177 of file FpgaRegs.h.

| #define FPGA_REG_FIRMWARE_REV 101 |

Definition at line 182 of file FpgaRegs.h.

| #define FPGA_REG_GENERAL_STATUS 91 |

Definition at line 153 of file FpgaRegs.h.

| #define FPGA_REG_HCLAMP_INPUT 10 |

Definition at line 71 of file FpgaRegs.h.

| #define FPGA_REG_HRAM_INPUT 6 |

Definition at line 65 of file FpgaRegs.h.

| #define FPGA_REG_HRAM_INV_MASK 8 |

Definition at line 68 of file FpgaRegs.h.

| #define FPGA_REG_HSKIP_INPUT 11 |

Definition at line 72 of file FpgaRegs.h.

| #define FPGA_REG_IMAGE_COUNT 18 |

Definition at line 80 of file FpgaRegs.h.

| #define FPGA_REG_INPUT_VOLTAGE 96 |

Definition at line 171 of file FpgaRegs.h.

| #define FPGA_REG_IO_PORT_ASSIGNMENT 51 |

Definition at line 120 of file FpgaRegs.h.

| #define FPGA_REG_IO_PORT_DIRECTION 50 |

Definition at line 117 of file FpgaRegs.h.

| #define FPGA_REG_IO_PORT_READ 90 |

Definition at line 150 of file FpgaRegs.h.

| #define FPGA_REG_IO_PORT_WRITE 49 |

Definition at line 115 of file FpgaRegs.h.

| #define FPGA_REG_LED_DRIVE 26 |

Definition at line 92 of file FpgaRegs.h.

| #define FPGA_REG_LED_SELECT 52 |

Definition at line 123 of file FpgaRegs.h.

| #define FPGA_REG_OP_A 2 |

Definition at line 35 of file FpgaRegs.h.

| #define FPGA_REG_OP_B 3 |

Definition at line 53 of file FpgaRegs.h.

| #define FPGA_REG_OVERSCAN_COUNT 17 |

Definition at line 79 of file FpgaRegs.h.

| #define FPGA_REG_POSTOVERSCAN_SKIP_COUNT 21 |

Definition at line 86 of file FpgaRegs.h.

| #define FPGA_REG_POSTROI_SKIP_COUNT 16 |

Definition at line 78 of file FpgaRegs.h.

| #define FPGA_REG_PRECLAMP_SKIP_COUNT 12 |

Definition at line 74 of file FpgaRegs.h.

| #define FPGA_REG_PREROI_SKIP_COUNT 14 |

Definition at line 76 of file FpgaRegs.h.

| #define FPGA_REG_ROI_COUNT 15 |

Definition at line 77 of file FpgaRegs.h.

| #define FPGA_REG_SCRATCH 53 |

Definition at line 135 of file FpgaRegs.h.

| #define FPGA_REG_SEQUENCE_COUNTER 105 |

Definition at line 188 of file FpgaRegs.h.

| #define FPGA_REG_SEQUENCE_DELAY 47 |

Definition at line 112 of file FpgaRegs.h.

| #define FPGA_REG_SHUTTER_CLOSE_DELAY 20 |

Definition at line 84 of file FpgaRegs.h.

| #define FPGA_REG_SHUTTER_STROBE_PERIOD 24 |

Definition at line 89 of file FpgaRegs.h.

| #define FPGA_REG_SHUTTER_STROBE_POSITION 23 |

Definition at line 88 of file FpgaRegs.h.

| #define FPGA_REG_SUBSTRATE_ADJUST 27 |

Definition at line 93 of file FpgaRegs.h.

| #define FPGA_REG_TDI_COUNT 54 |

Definition at line 137 of file FpgaRegs.h.

| #define FPGA_REG_TDI_COUNTER 104 |

Definition at line 187 of file FpgaRegs.h.

| #define FPGA_REG_TDI_RATE 48 |

Definition at line 113 of file FpgaRegs.h.

| #define FPGA_REG_TEMP_BACKOFF 60 |

Definition at line 143 of file FpgaRegs.h.

| #define FPGA_REG_TEMP_CCD 94 |

Definition at line 168 of file FpgaRegs.h.

| #define FPGA_REG_TEMP_COOLER_OVERRIDE 61 |

Definition at line 144 of file FpgaRegs.h.

| #define FPGA_REG_TEMP_DESIRED 55 |

Definition at line 139 of file FpgaRegs.h.

| #define FPGA_REG_TEMP_DRIVE 95 |

Definition at line 169 of file FpgaRegs.h.

| #define FPGA_REG_TEMP_HEATSINK 93 |

Definition at line 167 of file FpgaRegs.h.

| #define FPGA_REG_TEMP_RAMP_DOWN_A 57 |

Definition at line 141 of file FpgaRegs.h.

| #define FPGA_REG_TEMP_RAMP_DOWN_B 58 |

Definition at line 142 of file FpgaRegs.h.

| #define FPGA_REG_TEMP_REVISED 97 |

Definition at line 174 of file FpgaRegs.h.

| #define FPGA_REG_TEST_COUNT_LOWER 29 |

Definition at line 99 of file FpgaRegs.h.

| #define FPGA_REG_TEST_COUNT_UPPER 28 |

Definition at line 98 of file FpgaRegs.h.

| #define FPGA_REG_TIMER_LOWER 5 |

Definition at line 63 of file FpgaRegs.h.

| #define FPGA_REG_TIMER_UPPER 4 |

Definition at line 62 of file FpgaRegs.h.

| #define FPGA_REG_VFLUSH_BINNING 19 |

Definition at line 82 of file FpgaRegs.h.

| #define FPGA_REG_VRAM_INPUT 7 |

Definition at line 66 of file FpgaRegs.h.

| #define FPGA_REG_VRAM_INV_MASK 9 |

Definition at line 69 of file FpgaRegs.h.

| #define FPGA_TOTAL_REGISTER_COUNT 103 |

Definition at line 14 of file FpgaRegs.h.

KDE 3.5 API Reference

KDE 3.5 API Reference